Home > PCB のサイエンス > PCB 密度

生産の課題

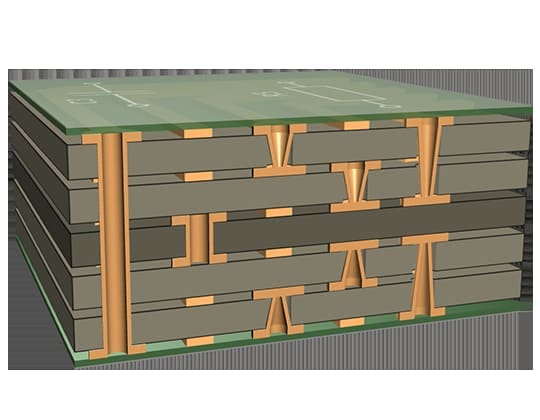

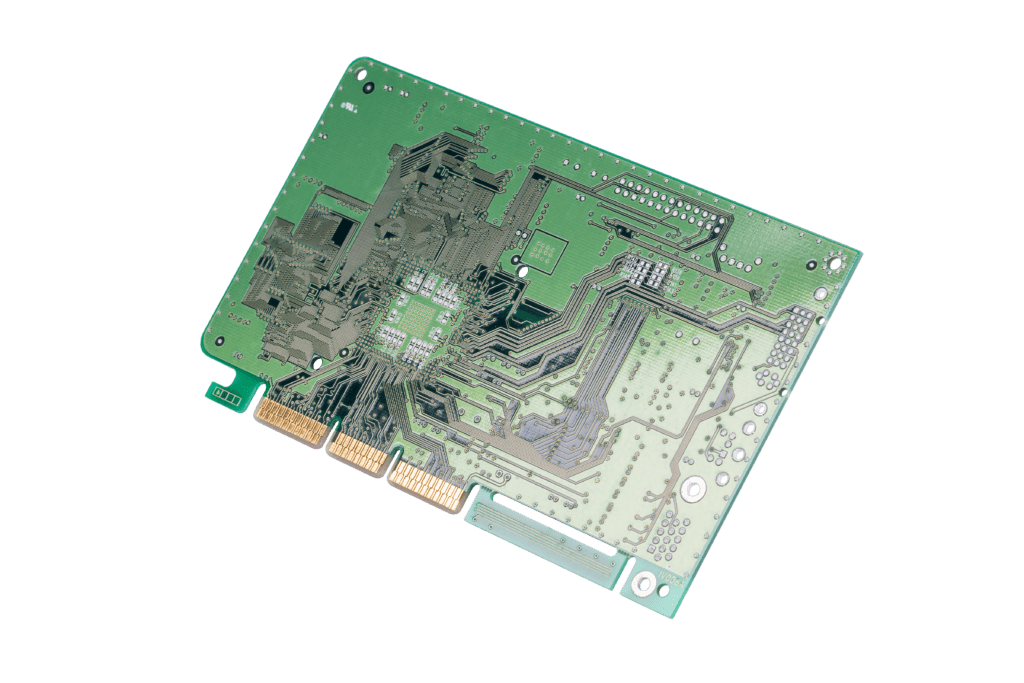

エレクトロニクスの進歩と小型化に伴い、HDI PCB の需要が大幅に増加していますが、プリント回路基板上の密度の上昇は、設計から生産に至るまでの課題です。 トレース間のスペースは最大 65µm です。 超複雑な設計ルールと製造プロセスを実現するために、HDI PCB は少なくとも 4 層、最大 24 層で作成され、ホールとビアによって相互接続されます。

ソフトウェアでの設計がエンジニアにとって困難な場合、生産における主な問題の 1 つは、めっき穴の信頼性を確保することです。 主な問題は、ビアとホール、およびめっきプロセスから発生します。 良好な穴メッキの完全性を確保するには、ブラインドビアのアスペクト比は 1:0.8 に制限され、 高度な値は 1:1 です。 標準的なプリプレグにはガラスファイバーも含まれており、レーザー穿孔には厚すぎます。 プリプレグに含まれるガラスがレーザーの方向を変化させ、これによりレーザービアホールの形状品質を劣ったまたは間違ったものにします。

主な機能

| HDI | 機能 |

|---|---|

| レイヤー数 MIN & MAX | 4-24L |

| HDIビルド 1+N+1, 2+N+2 | 3+N+3および任意の層 |

| 材料 FR4, ..., ETC. | 表参照 |

| 銅重量 MIN & MAX | 0.5オンス~6オンス |

| 最小トラック&ギャップ MM | 65/65μm |

| PCB厚さ MIN & MAX | 0.4-2.8mm |

| 次元 MAX | 0.457*508mm |

| 表面仕上げOSEP、ENIG、ETC。 | HASL、HASL LF、ENIG、無電解スズ、OSP、無電解銀、電気メッキ硬質金/軟質金、ゴールドフィンガー、選択的OSP、ENEPIG |

| メカニカルドリル MIN | 0.15mm |

| レーザードリル MIN | 0.076mm |

HDI PCB設計と信頼性の向上

良好なトラック定義を得るためにビルドアップにはより薄いベース銅を使用する必要があります。 (数多くのめっきプロセスにより銅の総厚が増加します)。 ベース銅の選択が、高周波アプリケーションの信号伝播にも影響を与える可能性があります。 プリペグ、ベース銅、および PCB の一層の薄型化が HDI PCB のトレンドになっています。

ビアホールはデリケートです。 ビアは組立プロセス中のリベットのようなものです。 RoHS プロセスでは、材料およびビアに高温ストレスがかかります。 Z 軸方向の材料の膨張はビアに応力をかけます。 ビア直径の削減と信頼性向上が、引き続きトレンドになっています。 さらに、組立プロセスはサーマルチョックの回数を増加させます。 この新たな状況下で、組立中にかかる力を軽減する唯一の方法は、より安定した FR4 を使用することです。 組立プロセス中や過酷な環境下での穴の破壊現象を制限したい場合は、低 CTE(熱膨張係数)材料が不可欠です。