Access the world's best network of PCB and technical parts manufacturers with the most optimized costs, expert engineering advice, short lead times, and sustainable processes.

Precision.

From design to delivery.

Why ICAPE Group?

ICAPE Group offers specialized solutions honed over 25 years of experience in the electronic industry. With a comprehensive product lineup encompassing all PCB technologies and various custom-made technical parts, our items are meticulously crafted and quality-controlled within our state-of-the-art factory network.

Our global infrastructure is strategically designed to optimize worldwide communication efficiency. Whether you require rapid online procurement or large-scale manufacturing, we provide end-to-end solutions that prioritize quality, reliability, competitiveness, and ultimately, customer satisfaction.

Realize your vision with precision and unwavering dedication by partnering with us

Technical Expertise

140 sales engineers specialized in all PCB and Technical Parts technologies

Advanced Manufacturing

80 carefully selected manufacturing partners in Asia, Europe, and South Africa

Quality First

Strict controls operated on production sites and inside our own laboratories

Logistics Solutions

Flexible shipment, storage, and local transport options worldwide.

Customer Service

300 representatives linked to our factories and experts to support our clients

Industries

ICAPE Group’s Power of Precision is found in the following industries:

Customer Testimonials

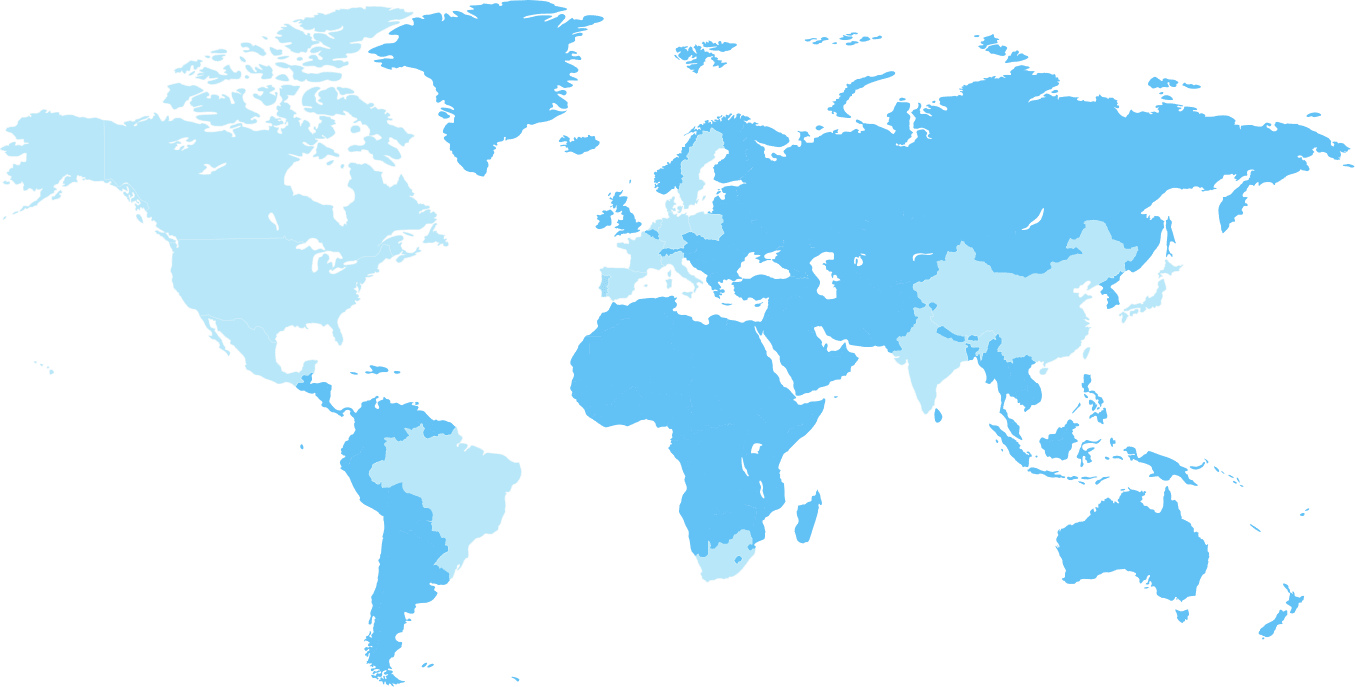

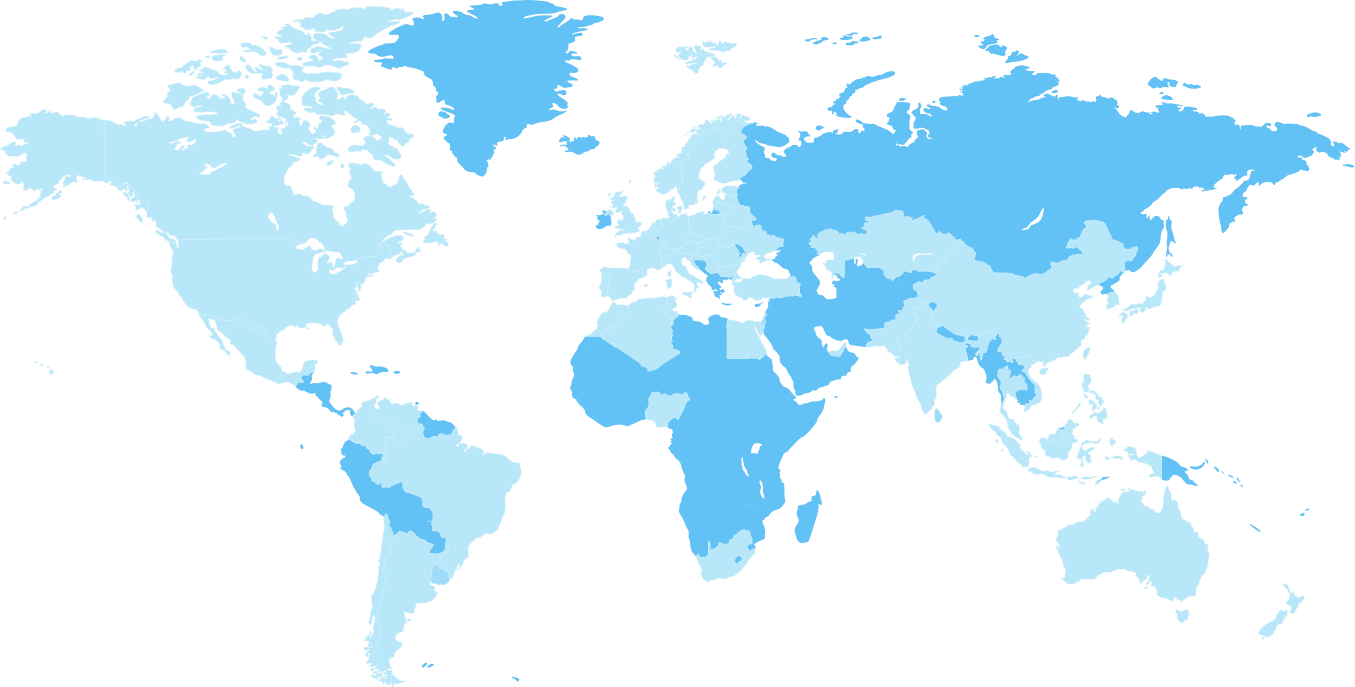

ICAPE Group worldwide presence

Find Your Local Expert - Contact Now!

Would you like to get in touch with a team from another country?

Select your country below

to find your best contact

Sustainability Engagements

ICAPE Group is committed to a CSR project to reduce the impact of its activities on the environment. We pay particular attention to the respect of human rights and we participate in various humanitarian and environmental actions with our corporate foundation ICAPE Planète bleue.

Take Advantage of the PCB Market

Hundreds of experts have already downloaded this free guide. You should too!

- Quarterly compilation of industry trends, insights, forecasts, and news

- Access to the latest developments in the industry, including material prices and cost comparisons

- Expert-curated information in a comprehensive format, all in one place

OUR NEWS

Employees Success Story : Klaus Moucha, a vibrant and dynamic new leader at ICAPE Group

Meet Klaus Moucha, a vibrant and dynamic new leader at ICAPE Group. With his optimism, humor, and unwavering determination, Klaus…

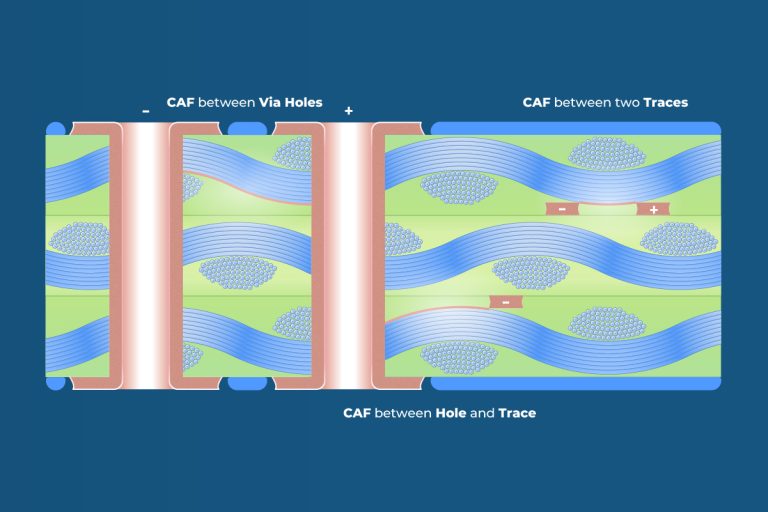

CAF : Understanding Conductive Anodic Filament (CAF) on PCBs

CAF : Understanding Conductive Anodic Filament (CAF) on PCBs Let’s explore a fascinating undesirable aspect of PCBs called Conductive Anodic…

Employees Success Story : Erika Leite, ICAPE Brazil Managing Director

In celebration of International Women’s Day, we are delighted to present an insightful interview with Erika Leite, a passionate and…